Design Solutions

Historically, design partitioning has always been a major concern for system architects, as the tasks to be performed needed to be allocated to either the software team to generate processor code, or to the specialist hardware team to realize functions in the programmable fabric. However, Open Computing Language (OpenCL) is a way to abstract the traditional hardware FPGA development flow so that software engineers can design hardware. The design is captured as C code for heterogeneous systems and the OpenCL runtime then breaks the data-parallel tasks and allocates them to hardware accelerators in the device.

The story of unmanned aerial vehicles (UAVs) has been one of uninterrupted technological progress over the last decade, and the segment remains one of the bright spots for military procurement moving forward. The steady advance in electro-optical (EO) imaging, radar, ultra-violet, and infrared sensors drives a pressing need for increased bandwidth on the wireless link.

Another key concern in UAVs is to minimize size, weight, and power (SWaP), but advances in programmable devices in both the logic and wireless domains can address these challenges. The requirement for wireless communications will vary with the type of vehicle, for example, UAVs the size of a small aircraft might connect via a satellite link to a controller on the other side of the world. In contrast, hand-launched machines would typically have a limited range and be transmitting to a local terrestrial based controller. Weight is a critical parameter, and there is a correlation with range and endurance for the UAV, and using the latest field programmable RF (FPRF) devices can reduce SWaP.

Programmable RF Devices Can Reduce SWaP

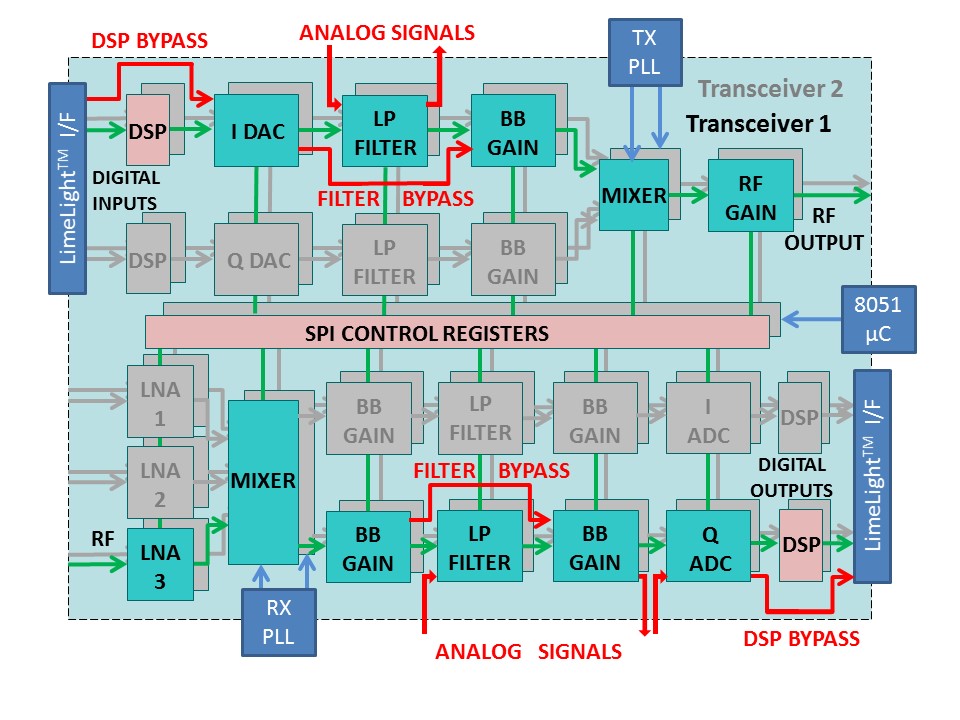

The highly integrated nature of the latest chips can save a multitude of external components, for example, the second generation FPRF, LMS7002M, contains two fully programmable transceivers. The digital data stream to be transmitted is first filtered by an on-chip programmable DSP to shape the spectrum, and a DAC generates an analog signal. This is further filtered and amplified before being passed to a mixer fed by a programmable local oscillator to create a carrier modulated by the input signal. A final stage of variable gain RF amplification provides the output signal from the chip.

The received RF signal is fed via a low noise amplifier (LNA) into a direct conversion mixer (sometimes called Zero-IF) to convert the RF to baseband. The baseband signal is filtered and amplified before being digitized by an on-chip ADC and then processed by programmable DSP before being output to the baseband chip.

Another weight-saving feature derives from the low power consumption of the FPRF, because the dual transceiver consumes less than a watt, and can be powered from a single supply rail. This frugal power requirement can be provided by a lighter power source, and the single rail saves the space, weight, and lower reliability associated with multiple voltage supplies.

The FPRF allows the payload weight budget to be met without sacrificing performance, which may be the driving factor in a UAV, where sophisticated sensors need a high bandwidth. FPRFs cover all frequencies from 100 kHz to 3.8 GHz in a continuous band, and the RF modulation bandwidth for each channel can be up to 160 MHz, yielding a baseband of 80 MHz. The primary reason that there are two channels is to support Multiple-Input Multiple-Output (MIMO), and for UAV applications MIMO techniques can be adopted to improve the link reliability. Both transmitters propagate the same data patterns, which add up constructively at the receiver, giving MIMO a more robust performance due to fading and interference, or under multi-path transmission conditions.

Figure 1: FPRF block diagram showing bypass options.

Some applications may require a tighter specification, say, for the filters, or higher resolution in the ADCs. The FPRF has been designed so that customers can utilize, supplement, or depower and replace any component, with bypass options and signal break-out points at all stages along the signal path.

The performance can be enhanced with the addition of LMS8001 devices, Up/Down RF frequency shifters, allowing the two channels to be tuned to different frequencies anywhere from 100 kHz to 12 GHz, giving a massive range of options. The two bands could be contiguous, but may also be widely different frequencies, with the result that the bandwidth can be doubled if required. Alternatively, one channel could be organized as a high capacity X Band satellite uplink, while the other is configured as a receiver for the downlink signal carrying command and control data.

Exploiting the real-time programmable nature of the FPRF allows the RF to be changed on-the-fly to provide frequency hopping to avoid detection, or interference. The control signals can be computed and fed to the device by an FPGA.

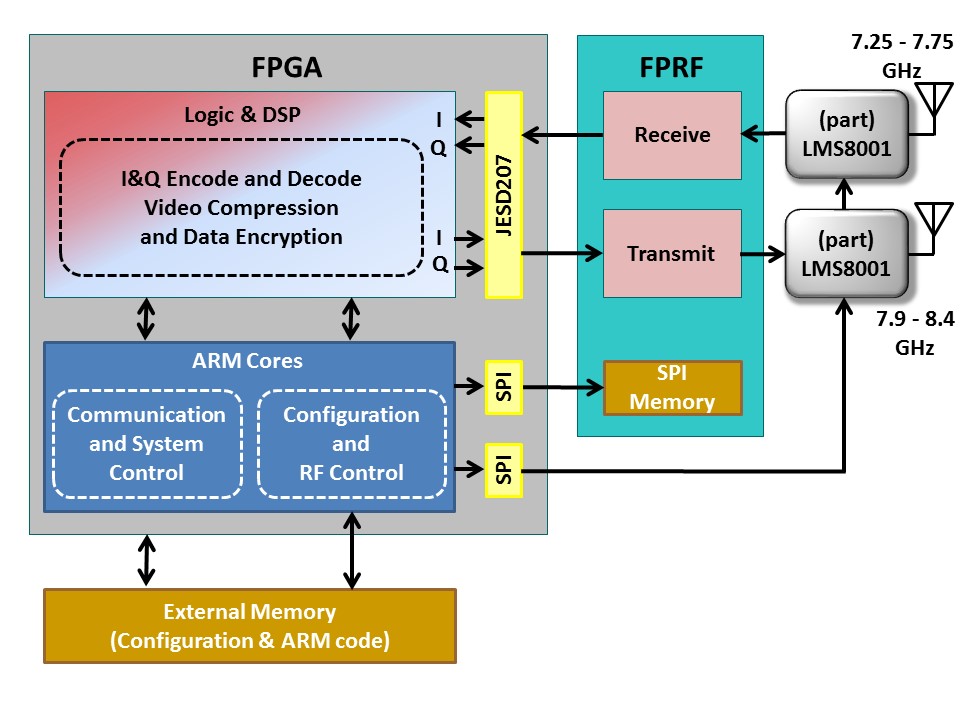

Figure 2: Concept for UAV wide band satellite communication.

FPGAs Provide the Baseband Functions

A baseband chip works in conjunction with the FPRF to form the complete wireless subsystem. Although processors can perform many of the tasks required, they are considerably slower and not as power efficient as hardware based systems at computationally complex tasks. For this reason, the compute intensive jobs of encoding and decoding are ideal for the FPGA fabric, and are the solution of choice. The logic can format the sensor data to make it suitable for transmission in any of several complex modulation schemes such as OFDM, WCDMA, QPSK, or QAM. The baseband chip needs to resolve data into the in-phase and quadrature (I&Q) component ready to modulate the RF carrier. Conversely, once decoded, the communication and control signals to fly the UAV are well-suited to the ARM cores that feature on some FPGAs. An ARM processor can also load encryption keys into a crypto core buried inside the FPGA fabric, plus directly control the FPRF by programming the SPI memories.

FPGAs are manufactured with a range of capabilities suited to a variety of different tasks. Low-cost devices can format and decode the data, while in high-end FPGAs the logic resources can be employed to compress and encrypt the video stream prior to encoding. In addition, the high performance ARM cores may be used for running sense-and-avoid algorithms.

For very secure systems, the field programmability of both FPGAs and FPRFs can be exploited to set parameters immediately prior to flight. The RF frequencies of the links and the encryption key could be loaded into memory that the ARM core reads, and security is also enhanced because both products store their configuration in volatile memories. In the event that the UAV crashes or is captured, critical details of its operation can be safeguarded by simply removing power.

Filed Under: Aerospace + defense