By Matt Romig, Analog Packaging, Productization Manager, Texas Instruments

As feature sizes shrink on component packaging, printed circuit boards need not become more complex.

Miniaturization has improved the quality and breadth of data to allow for broadband nearly everywhere: 3G to your mobile device, high definition on your TV, and integrating more features into a single device or data source. Nowhere is this truer than in component packaging, where miniaturization and integration allow devices to be smaller, more powerful and more efficient in their creation and implementation.

Figure 1: Leaded packages

Trends in component packaging miniaturization have been to smaller outlines, finer pitches, and area array rather than peripheral lead. Also leadless rather than leaded, from fan out to fan in, as well as thinning and combining multiple ICs or passives within the package or stacking packages. Some examples of packaging technologies that enable these trends are ball grid array (BGA), wafer chip scale packaging (WCSP), and quad flat no-lead (QFN). These packages are commonly being used in mobile applications, but they are increasingly being used in other consumer or infrastructure applications as well.

These component packaging miniaturization trends result in greater challenges for OEMs of consumer or infrastructure applications. Typically OEMs have two main concerns. The first and most common is that they want to continue to use standard or low-cost PCBs. Second is that they do not want to significantly upgrade their equipment for PCB assembly. For this reason, often there are arbitrary limits or rules of thumb about packaging types or features.

Miniaturized packaging options

Historically, most components were packaged in leaded packages in gull-wing or through-hole configurations such as dual inline package (DIP), quad flat pack (QFP), or small outline package (SOP). Some examples of these can be seen in Figure 1. These packages have enabled some level of miniaturization through reduced pitch, width and thickness, such as thin quad flat pack (TQFP) or thin shrink small outline package (TSSOP). However, these packages have run up against fundamental limits based on the lead pitch rules, which vary from 1.27 mm down to 0.5 mm, or in some cases 0.4 mm or less.

Ball grid array (BGA) packages are the most common version of area array packages. BGAs are a huge enabler for miniaturization because they allow pins to be placed in a full area under the component, rather than just on the periphery. In highly miniaturized configurations BGAs are often called chip scale packages (CSPs) because the packaged component is shrunk to nearly as small as the IC itself. Several examples of BGA packages include plastic substrate-based (PBGA, FBGA, TBGA) or wafer scale (DSBGA, WCSP, WSP). Several illustrations can be seen in Figure 2. The various formats enable many miniaturization features such as electrical performance, highest possible I/O density, and manufacturing efficiency. Typical lead pitch for BGA packages can range from 1.27 mm down to 0.4 mm.

Figure 2: BGA Packages

Leadless packages are a rapidly growing technology as they are constructed similarly to leaded packages, but eliminate the exposed leads. There are several trade names, but the most common basic terms are quad flat no-lead (QFN), or small outline no-lead (SON). Several examples can be seen in Figure 3. The component assembly methods developed for leadless packages enabled many important features for miniaturization such as electrical performance, thermal performance and manufacturing efficiency. Typical lead pitch for leadless packages can range from 0.65 mm down to 0.4 mm.

Figure 3: Leadless packages

OEM concerns

The biggest contributors to the cost of a PCB are the number of layers (meaning more process steps in manufacturing the PCB), and the design rules such as lines, spaces, and via sizes (meaning slower throughput or lower yield in the PCB manufacture). When finer features are needed, a different class of PCB stack-up is used. This is often referred to as high-density interconnect (HDI). This advanced process starts with a standard core created using thick, rigid layers with mechanically drilled vias. Then HDI layers are added, which are thinner and have finer features and laser drilled vias.

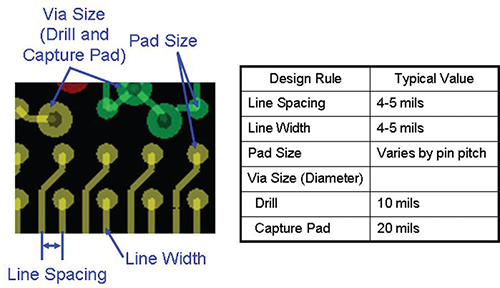

While the exact rules and constructions may vary, a standard or low-cost PCB typically uses a line-width and spacing of 4-5 mils (100-125 μm); and vias, which are 8-10 mils (200-250 μm) in drilled diameter, and have a capture pad of 18-20 mils (450-500 μm). These are illustrated in Figure 4. Some common terms for these features are phrases like 4 mil line and space or a 20/10 via. Features that are finer than this are generally considered as adding cost and possibly requiring HDI technology. So any miniaturized component to be used on a low-cost PCB must be capable of being routed out using these design rules.

The second biggest concern for OEMs is the capability to use their existing manufacturing base for assembly. Some common concerns are the accuracy required by the placement machines, the solder printing methods, the accuracy required of the solder stencils, and the ability to ensure and inspect for a high-quality joint formation.

Figure 4: Example design rules for a low-cost PCB

While the capability of every factory and equipment set varies, there are many cases where the equipment set is capable of implementing more miniaturization than is presently being used. One example of a manufacturing method that is limited is wave soldering, where the bottom of the PCB is immersed in solder. Thus, packages with features like area array interconnect or thermal pads require customization of component placement and soldering techniques. Nearly all methods using printed solder paste for established gull-wing packages such as TSSOP and TQFP, especially those with some level of X-ray inspection for thermal pads or other large devices like ASICs or FPGAs, should be fully capable to handle many miniaturized packages, provided these packages and processes are carefully considered to meet capability, quality, and throughput requirements. Table 1 shows a basic comparison of surface mount technology (SMT) capability for the miniaturized packages mentioned previously.

Often there are other concerns for OEMs that are application specific. Several examples are the lifetime fatigue performance of the solder joints (temperature cycle reliability), drop test performance, standoff height, or heat sink compatibility. These elements are important to consider, but are hard to describe generically because of the specific application requirements.

Designing for miniaturized packages

Because of the familiarity with the historical leaded packages, and the aggressive implementation of miniaturized packages in mobile applications that typically set the pace for the rest of the industry, there are many assumptions or rules of thumb about what type or pitch of packages can be implemented on a PCB. In many cases, there may be an opportunity for the component supplier and OEM to work together to find a solution that will enable miniaturization without raising PCB cost by considering and adjusting the specific factors challenging one of the limitation areas.

One helpful approach for PCB designs can be to consider the desired PCB rules and features as part of the component package design. In practice, OEMs communicate with component suppliers to share their desired design rules (lines, spaces, vias, etc.). With this communication, the component suppliers can be sure to design the component packaging with PCB routability in mind. It may be valuable for the component supplier to prepare and even deliver a basic PCB design rule diagram as part of the documentation for the component. An example is shown in Figure 5 for a component in a BGA package. This illustrates the case where a typical rule of thumb would say that 0.5 mm or 0.65 mm pitch BGA could not be used on a low-cost PCB. However, careful design by the component supplier using the targeted OEM design rules can achieve a realistic implementation. Note that other PCB layout constraints or device electrical requirements may also factor into this approach.

Figure 5: Example component basic routability diagram

For PCB assembly, the best approach is to consider the specific capability required in order to accurately handle the component pitch. For solder printing, component datasheets or application notes generally contain recommendations for solder stencil design, which are usable on most equipment. For component placement, the historical capability as established on leaded packages is a good reference point. For example, if a TSSOP or QFP package at 0.5 mm pitch can be placed, then it is very likely that a BGA or leadless package at 0.5 mm pitch also could be placed. In both cases, it may be more practical and inexpensive for the component supplier to provide mechanical samples and perhaps even an evaluation module (EVM) board, for the factory to evaluate in advance of the real component.

Texas Instruments

www.ti.com

::Design World::

Filed Under: Packaging, ELECTRONICS • ELECTRICAL

Tell Us What You Think!